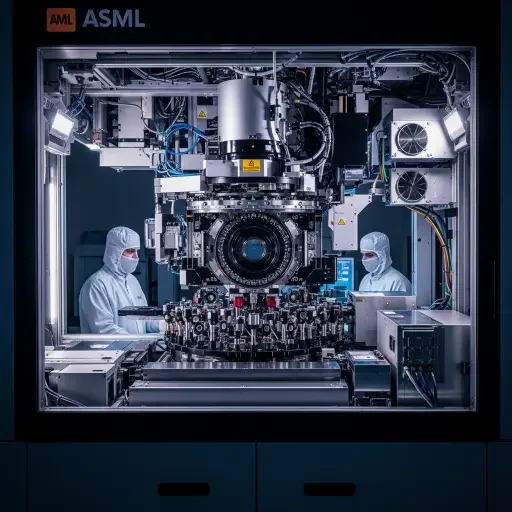

Every semiconductor cycle hides a timing problem: the longest‑lead equipment makers — the custodians of technical moats — must anticipate capital spending that, by the time it materializes, has already reshaped product roadmaps. ASML, the owner of extreme‑ultraviolet (EUV) lithography, is the archetypal example. Its machines are not interchangeable parts; they are architectural anchors. That makes ASML a platform power, but also a market that depends on synchronous cap‑ex waves from foundries and memory makers. The plausible upside emerges if two things happen at once: DRAM manufacturers scale EUV adoption and TSMC resumes a new tranche of orders.

![]()

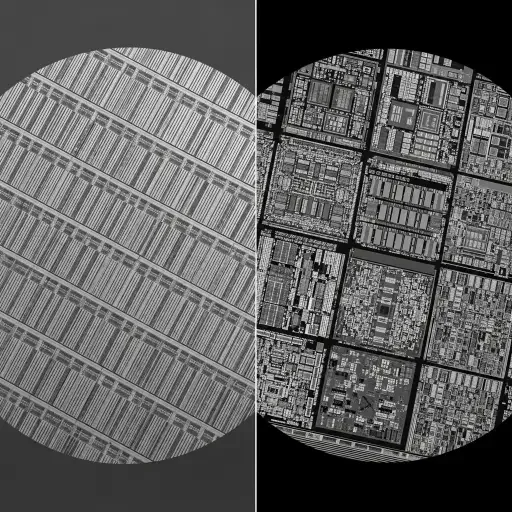

Why does DRAM matter to ASML? Historically, DRAM fabrication has leaned on immersion lithography and multi‑patterning; EUV adoption was selective because cost per wafer and process maturity mattered more than density gains. That logic is changing. As memory makers pursue tighter nodes and higher bit densities to service AI training sets and high‑bandwidth compute (HBM stacks, large cache pools), EUV becomes not merely nice-to-have but economically compelling: it reduces mask complexity, shortens tool chains, and — crucially — improves yield curves at advanced pitches.

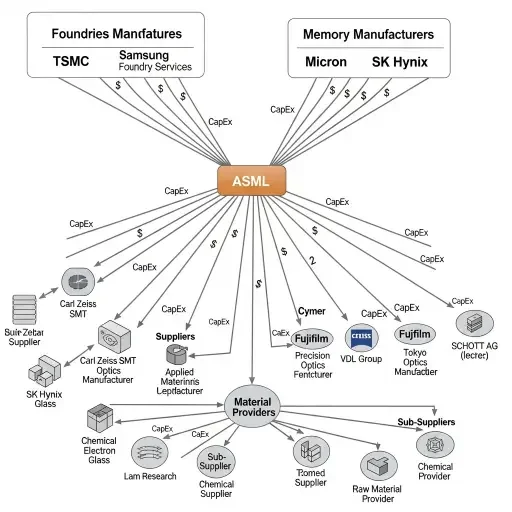

A DRAM vendor publicizing an EUV development roadmap is not just a technical blip. It’s a commitment that pulls orders forward across the supply chain — deposition tools, etchers, photomask houses, and ultimately ASML’s EUV scanners. The cap‑ex multiplier here is structural: each EUV scanner enables high‑volume production that requires an ecosystem upgrade. If multiple DRAM players accelerate EUV pilots into mass production, the aggregate demand for EUV machines could become a material incremental revenue stream for ASML over a 24–36 month horizon.

Layer two of the upside is TSMC. Foundries were ASML’s reliable tailwind for years; TSMC’s node transitions are an order book engine. After a period of inventory digestion and muted orders, TSMC restarting substantial equipment purchases would reintroduce a second, sometimes larger, demand vector. The critical nuance: TSMC’s orders are not fungible with DRAM demand in timing or maker profile. Foundry EUV needs often come in fewer, well‑timed system batches tied to specific node introductions, while DRAM demand scales with product cycles and wafer starts.

The intersection matters because cap‑ex cycles cascade. Suppliers upstream (optical subsystems, wafer stage manufacturers, vacuum components) experience order volatility that amplifies downstream. When both DRAM and TSMC order, lead times lengthen and supplier pricing power rises. For investors, that creates margin leverage — not just for ASML but for its supply chain. A coordinated cap‑ex wave reduces the risk profile embedded in ASML’s forward guidance: backlog becomes more durable; unit economics improve as fixed R&D and production overhead is spread across more systems.

But the upside is constrained by three practical checks.

-

Inventory and digestion. Memory customers hold inventory buffers. Even with strategic node shifts, a measured order cadence is likely while DRAM makers clear current stocks. The key metric: wafer starts and bit‑growth versus inventory days. A rapid decline in inventory days while wafer starts rise is the pulse test for near‑term OEM orders.

-

Yield maturity. EUV in DRAM is not a flip switch. Early pilots must demonstrate stable yields at target pitches. Yield deltas — the percentage improvement in good dies per wafer — dictate whether the higher CAPEX of EUV pays off. Watch yield announcements, reticle error reports, and cycle time metrics from suppliers who probe yield sensitivity.

-

Capital allocation at customers. TSMC and memory players triage investment just like public investors triage portfolios. If macro uncertainty or end‑market softness persists, fab spending can be delayed even when technological incentives are present. Expect staged rollouts: pilots → small‑scale orders → volume orders. The staging creates optionality for ASML but also delays liquidity conversion.

For investors the practical playbook is simple and information‑engineered: watch the leading indicators that convert narrative into orders.

- Supplier order books: optical and motion subsystem makers report NHS (new‑hardware sales) trends earlier than OEMs.

- Reticle and mask makers: increased mask complexity or higher mask counts per layer suggest multi‑patterning persistence; a declining mask count per layer implies EUV substitution.

- Wafer start data: memory wafer starts versus inventory days (from industry analysts) reveal cadence shifts.

- TSMC Capital Plans and equipment tender notices: filings and supplier confirmations can preannounce tranche timing.

- Yield metrics from pilot lines: internal yield improvements are the binary between pilot and volume.

If these signals align — falling mask counts, rising wafer starts, supplier order acceleration, and positive pilot yields — the probability of a sustained ASML upside meaningfully increases. That scenario compresses uncertainty: backlog becomes visible, supply chain pricing improves, and investors can model higher near‑term revenue with lower execution risk.

ASML’s moat is both its strength and its timing puzzle. Platform dominance gives it pricing power; but that power only translates into growth when capital cycles among its customers align. A DRAM embrace of EUV plus a renewed TSMC ordering cycle would be that alignment. For allocators, the margin of safety is watching the chain above and below ASML — from mask houses to wafer fabs — for synchronous signals that cap‑ex is shifting from optional to necessary.

ASML’s upside is credible but conditional. The company sits at the nexus of technological necessity and cyclical capital. If DRAM makers scale EUV and TSMC restarts a tranche of orders, expect cascading cap‑ex effects that lift ASML and its suppliers. The actionable principle: monitor upstream supplier orders, mask count trends, wafer starts, and pilot yields — these are the low‑entropy signals that convert the hypothesis into investable reality.

Tags

Related Articles

Sources

ASML earnings reports and guidance; TSMC and DRAM manufacturer capex announcements; semiconductor industry analysis from Bloomberg, Reuters, and Financial Times; supplier chain data and memory market research.